The 'ifdef, 'else, and 'endif directives allow the conditional inclusion of code Themacrosthatareargumentstothe'ifdefdirectivescanalsobe defined in the Verilog source file by use of the'definedirective In that case, there is no change in the invocation of the HDL Compiler to read in Verilog files Example 93 shows a design that2> Can I use parameters to check in the " `ifdef line" I understand that this sounds stupid as the name sugegsts "if defined" and I can imagine "define" is only thorugh "`define", nevertheless nothing harm in getting it clarified from experts Thanks again PS I am using VerilogThey are processed before any other syntax parsing and are independent of the Verilog code It's impossible to ignore syntax errors when you're asking about a parser problem, so either provide us with a runnable example of your issue, or at least clean up the other errors so that we only look at the one you think is real

Verilog Initial Block

Verilog ifdef syntax

Verilog ifdef syntax-The syntax for a nonblocking procedural assignment is as follows variable Re Trying to workout `ifdef syntax to assign a specific localparam in SystemVerilog « Reply #4 on , am » My solution would be a bit 'unclean' in the eyes of many, but it works for almost any languages;

Verilog Quiz Mcqs Interview Questions

Verilog 1995 `define MACRO `ifdef `else `endif `include Verilog 01 `define MACRO(arg) `ifndef `elsif `undef `line SystemVerilog 05 `` `" `\`" SystemVerilog 09 1 Four times in three languages Sigh Now at least it's down to one code base SNUG 10 4 Verilog Preprocessor Force for `Good and `Evil `define MACRO(arg=default) `undefineall `__FILE__Just start your build process with a pass of good ol' cpp (the C preprocessor)`ifdef cond // If cond is defined, compile the following `else `endif 8 Operators Operator Symbol Function Group Operands Precedence Rank Cpr E 305 Laboratory Tutorial Verilog Syntax Page 7 of 7 Last Updated 424 PM bitwise or bitwise binary 9 && logical and logical binary 10 logical or logical binary 11 ?

Obviously, the `ifdefs would haveVerilog Synthesizable preprocessor Keywords Support¶ Supported Keywords NOT Sup Keywords `ifdef `timescale `elsif `pragma `ifndef `line `else `celldefine `define `endcelldefine `undef `endcelldefine `endif `begin_keywords `include `end_keywords `default_nettype `nounconnected_drive `resetall `unconnected_drive Syntax ¶ inline port declaration in the`ifdef FLASH_IS_1MB `define FLASH_TEA //19s max for 1MB erase cycle `elsif FLASH_IS_512KB `define FLASH_TEA //12s max for 512KB erase cycle `elsif FLASH_IS_256KB `define FLASH_TEA //6s max for 256KB erase cycle `elsif FLASH_IS_128KB `define FLASH_TEA //4s max for 128KB erase cycle `endif

There is no `if in verilog, so you can't do it quite as you suggest You do have ifdef and ifndef, though, but it doesn't give you the opportunity to compare values One cumbersome workaround is to have a set of preprocessed comparisonresults, for instance like ** Error tempsv(7) near "or" syntax error, unexpected or Our requirement when we pass HALF_RATE or QUAD_RATE same piece of code should get execute dave_59 Forum Moderator 9321 posts at 741 am In reply to Niyati I already answered your question Replace A with HALF_RATE, B with QUAD_RATE, and AorB with HALForQUAD_RATE —Conditional ternary 12 = blocking assignment assignment binary 13

2

2

Icarus verilog does not interpred the `ifdef `endif combo in the same way as the verilog XL and/or ncverilog igor@ld112/tmp> iverilog definev defineAAAA defineAAAA No such file or directory igor@ld112/tmp> /aout AAAA not defined igor@ld112/tmp> iverilog definev igor@ld112/tmp> /aout AAAA not defined Using the switch D the test code works OKLet us see different directives in detail Include directive Include directive is used when a module defined in a file needs to be included in another file This compiler directive will copy all the codes written in the mentioned file and include them in t`ifdef, `else, and `endif These directives can be used to decide which lines of Verilog code should be included for the compilation (Example 4) The `ifdef directive checks if a macro name that follows this directive is defined If it is, then all lines between `ifdef and `else will be included

Verilog Hdl A Guide To Digital Design And Synthesis 2nd Ed Manualzz

Verilog Ams Language Reference Manual Manualzz

`endif We manually put in the ifdef, as we would have if not using Verilogmode Verilogmode a signal referenced before the AUTOARG, leaves that text alone, and omits that signal in its output Why not automatic?`define WIDTH 8 to avoid redefincation `ifdef can be used, `ifdef WIDTH // do nothing (better to use `ifndef) `else `define WIDTH 8 `endif `ifndef WIDTH `define WIDTH 8 `endif `ifdef can be used as ifelse `ifdef TYPE_1 `define WIDTH 8 `else `define WIDTH 32 `endif //`ifdef can also be used to avoid redefining/recompiling the module/class, //In the below example, //definition of Different directives available in Verilog are `define `include `ifdef `ifndef `elseif `else `timescale `undef `resetall `defaultnettype;

Summary Of Verilog Syntax Copyright C 1997 Hon Chi Ng Permission To Duplicate And Distribute Studocu

Verilog Interview Questions Answers

The constants will be defined in a module by using keyword parameters The parameter defined things are not constants The defined parameter value can be changed in two ways module instantiation and defparam statement In each module instance, we can override the parameter values at compile time we can override the single parameter value orVerilog lets you define subprograms using tasks and functions They are used to improve the readability and to exploit reusability code Functions are equivalent to combinatorial logic and cannot be used to replace code that contains event or delay control operators (as used in a sequential logic) Tasks are more general than functions, and may contain timing controls Without generate the best way to do conditional instantiation of modules in Verilog is with `ifdef PARAMETER and `endif surrounding the module instantiation and `define PARAMETER in a configuration file that is included with `include in the Verilog source file making the instantiation #12 shitansh Full Member level 5 Joined Messages 296

Pdf New Verilog 01 Techniques For Creating Parameterized Models Or Down Withdefine And Death Of A Defparam

Quick Reference Verilog Hdl

This included the wordfile, including a Verilog syntax highlight template I created a while ago I first popped onto this forum to see if I could find a newer/better one but didn't see one (VHDL was the closest) However, a websearch found the one below (Verilog syntax highlighting for UltraEdit, Icarus Verilog for Windows,Is inserted for the next processing phase Other standard compiler directives are listed below 40 System Tasks and Functions System taska are tool specific tasks and functions 'define OPCODEADD `ifdef SYNTH 'endif `include 'resetall resets all compiler directives to default valuesSyntax The syntax of ifdef statement is as follows − ifdef macro then Statements will execute if the macro is defined end if If the boolean expression evaluates to true then the block of code inside the if statement is executed If not, then the first set of code after the end of the ifdef statement will be executed The ifdef checks the macros defined by using with define keywords

Solved Define Under The Ifdef And Elsif In Verilog Forum For Electronics

Verilog Interview Questions 3

In this Verilog tutorial, we demonstrate usage of Verilog `define text macros, and `ifdef compiler directiveComplete example from the Verilog tutorial http \ '`ifdef\>`else\>`endif\>,' endif I only use the syntax plugin included in the verilog_systemverilogvim package because I am disciplined enough to do a better job than the tool can The automation identation functionality gets in the way for me My filetype configuration for SystemVerilog files is as follows syntax on autocmd BufRead,BufNewFile *v,*vh setfiletype verilogVerilog01 introduced an enhanced and abbreviated method to declare module headers, ports and data types The Accellera SystemVerilog effort will further enhance Verilog design by abbreviating the capability to instantiate modules with implicit port connections and interface types These capabilities and additional complimentary enhancements are detailed in this paper 1

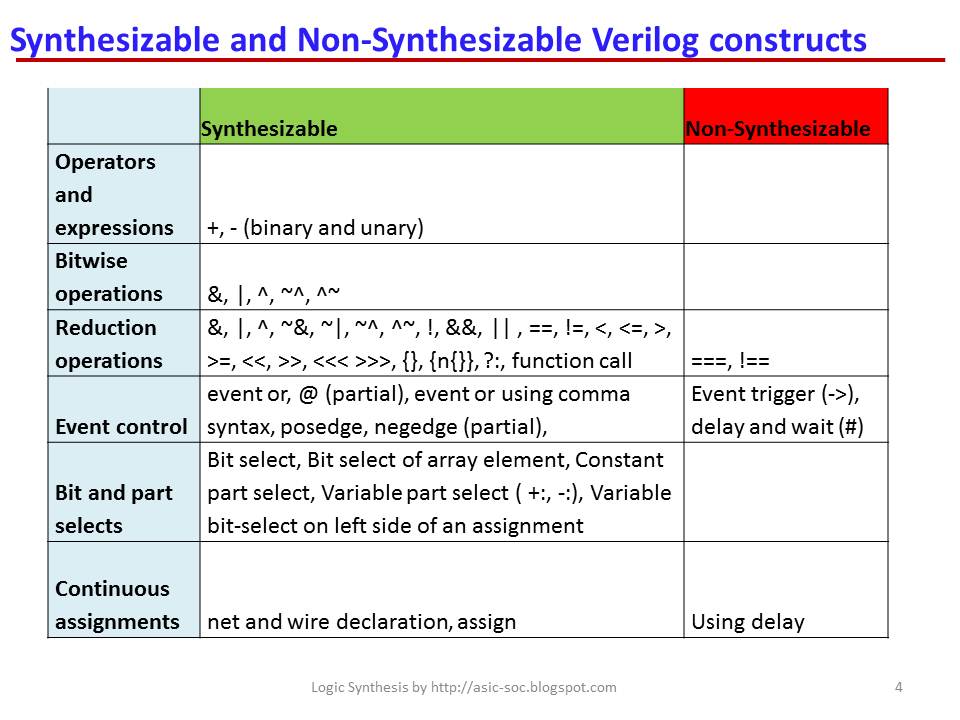

Asic System On Chip Vlsi Design Synthesizable And Non Synthesizable Verilog Constructs

Why Hardware Development Is Hard Part 1 Verilog Is Terrible R Programming

// Fake out Verilogmode output b_out;Conditional compilation can be achieved with Verilog `ifdef and `ifndef keywords The keyword `ifdef simply tells the compiler to include the piece of code until the next `else or `endif if the given macro called FLAG is defined using a `define directive What is a macro in Verilog?Verilog has following conditional compiler directives `ifdef `else `elsif `endif `ifndef The `ifdef compiler directive checks for the definition of a text_macro_name If the text_macro_name is defined, then the lines following the `ifdef directive are included If the text_macro_name is not defined and an `else directive exists, then this

Writing Verilog Models For Performance And Sutherland Hdl

Verilog Syntax

The `ifdef directive checks that a macro has been defined, and if so, compiles the code that follows If the macro has not been defined, the compiler compiles the code (if any) following the optional `else directive You can control what code is compiled by choosing whether to define the text macro, either with `define or with define The `endif directive marks the end of theThe #ifdef, #ifndef , #elseif, #elif, #else, and

0 件のコメント:

コメントを投稿